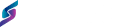

سازمان PCI‑SIG نسخه ۰٫۵ پیشنویس PCIe 8.0 را منتشر کرد که نقطه عطف مهمی در مسیر توسعه این استاندارد با پهنای باند 1 ترابایت بر ثانیه به حساب میآید.

به گزارش سرویس سخت افزار تکناک، این سازمان مسئول نظارت بر توسعه استاندارد PCIe و استانداردهای مرتبط با آن است. نخستین پیشنویس مشخصات PCIe 8.0، الزامات معماری را تعیین میکند و به اعضای PCI-SIG امکان میدهد نمونهسازی اولیه را آغاز کنند و پیشنهادهای نهایی خود را ارائه دهند.

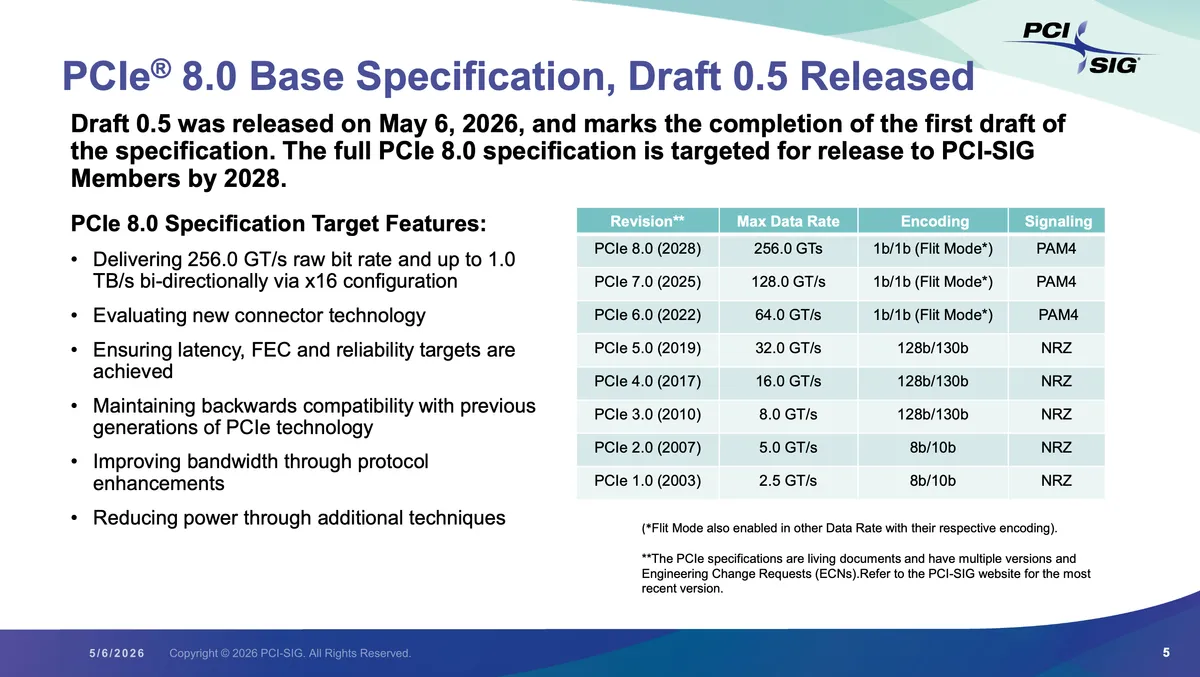

نسخه 0.5 تأیید میکند که نرخ انتقال داده در این رابط جدید به 256 گیگاترنسفر بر ثانیه خواهد رسید؛ رقمی که در پیکربندی x16، پهنای باندی دوطرفه تا سقف 1 ترابایت بر ثانیه را فراهم میکند.

نسخه 0.5 استاندارد PCIe 8.0 نخستین پیشنویس کامل این مشخصات است که اهداف مفهومی و سازوکارهای کلیدی را تثبیت میکند و تمامی جنبههای اصلی معماری از جمله بخشهای الکتریکی، منطقی، انطباقپذیری و نرمافزاری را مشخص مینماید. این موضوع به معنای آن است که PCI-SIG همچنان نرخ بیت هدف 256 گیگاترنسفر بر ثانیه، سیگنالدهی PAM4 همراه با تصحیح خطای پیشرو یا FEC و کدگذاری Flit Mode، بهبودهای پروتکلی برای افزایش پهنای باند، سازگاری با نسلهای قبل و فناوری کانکتور جدیدی را که هماکنون در حال ارزیابی است، حفظ کرده است. با وجود این، از آنجا که نسخه 0.5 پیشنویس نهایی محسوب نمیشود و همه بخشهای مشخصات تثبیت نشدهاند، برخی پارامترهای الکتریکی و بهینهسازیهای پروتکلی همچنان قابلیت تنظیم و بهبود بیشتر دارند.

مرتبط: اولین SSD جهان با استاندارد PCIe 6.0 رکورد سرعت ۲۸ گیگابایت

مرتبط: مادربرد جدید MSI با قدرتی فراتر از نسل قبل معرفی شد

انتشار این نسخه یک نقطه عطف مهم به حساب میآید، چرا که از این مرحله به بعد طراحان سختافزار، از شرکتهای بزرگی مانند AMD، اینتل و انویدیا گرفته تا تأمینکنندگان IP یا PHY، میتوانند کار روی نمونههای اولیه و طراحی معماری را آغاز کنند، هرچند همچنان باید برای تغییرات احتمالی برنامه جایگزین داشته باشند. نکته کلیدی این است که مشخصات به اندازه کافی به بلوغ رسیده و امکان شروع توسعه فراهم شده است.

بر اساس گزارش تامز هاردور، یکی از بخشهای قابل توجه این اعلامیه آن است که PCI-SIG همچنان در حال ارزیابی فناوری کانکتور جدید است؛ موضوعی که نشان میدهد لایه فیزیکی مبتنی بر مس فعلی به طور نگرانکنندهای به محدودیتهای خود نزدیک شده است.

بودجه تلفات سیگنال، تداخل متقابل و بازتابها در استانداردهای PCIe 5.0 و 6.0 به چالشهای جدی تبدیل شدهاند، اما در PCIe 8.0 با نرخ بیت 256 گیگاترنسفر بر ثانیه (سرعتی که تاکنون هیچ استاندارد مبتنی بر مس به آن دست نیافته است) این مشکلات احتمالا به کابوسی واقعی تبدیل خواهند شد. در چنین سرعتهایی، کانکتور لبهای سنتی و مسیرهای مادربرد ممکن است بدون مصرف توان بسیار بالا برای اکولایزیشن یا افزایش تأخیر ناشی از FEC نتوانند یکپارچگی سیگنال قابل قبولی ارائه دهند. در نتیجه، PCI-SIG ممکن است به سمت بازطراحی اسلاتهای PCIe با استفاده از مواد بهتر و تلرانسهای دقیقتر حرکت کند، یا بار دیگر مسیرهای الکتریکی را کوتاهتر کند و تعداد ریدرایورها در هر لینک را افزایش دهد. با وجود این، از آنجا که PCI-SIG قصد دارد سازگاری با نسلهای پیشین را حفظ کند، نباید انتظار تغییرات اساسی در سطح کانکتور را داشت.

با انتشار این پیشنویس، استاندارد PCIe 8.0 مسیر خود را برای تصویب نهایی در سال 2028 ادامه میدهد.

مرتبط: رونمایی کوالکام از نسخه جدید ۷ هستهای پردازنده اسنپدراگون ۸ الیت