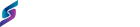

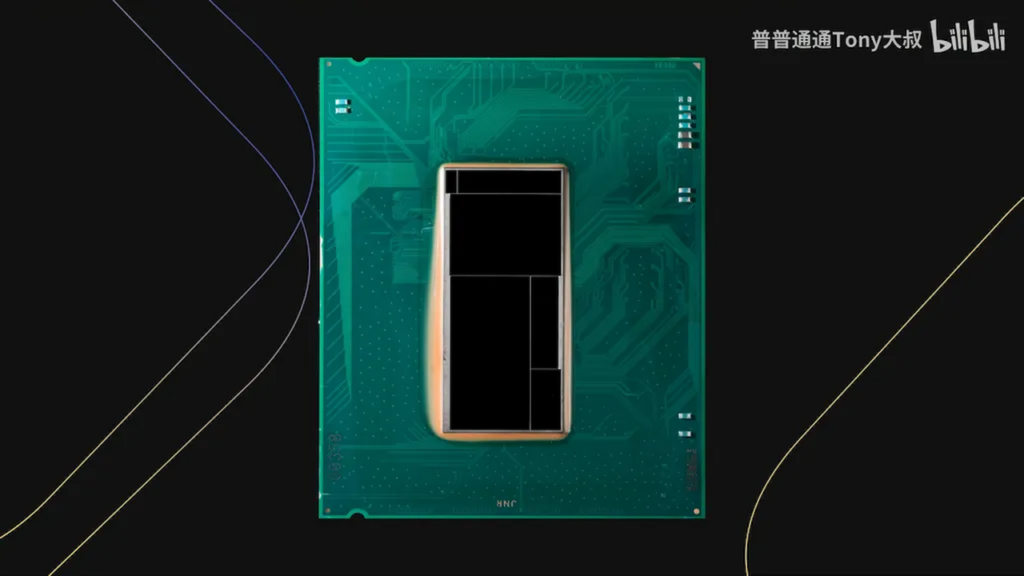

ایسوس تصاویر دقیقی از هسته (Die) پردازنده Core Ultra 9 285K اینتل منتشر کرد. این تصاویر رویکرد جدید اینتل در طراحی پردازندهها را بهنمایش میگذارند.

بهگزارش تکناک، ایسوس بهتازگی تصاویر رسمی از Die شاتهای پردازنده Core Ultra 9 285K مبتنیبر Arrow Lake اینتل را منتشر کرده است. این تصاوی معماری Chiplet یا Tile در Arrow Lake را دقیق بررسی میکنند که با استفاده از فناوری پیشرفته بستهبندی سهبعدی Foveros اینتل ساخته شده است.

تامزهاردور مینویسد که در طراحی Arrow Lake، شش Tile اصلی شامل Compute Tile و SoC Tile و IOE Tile و Graphics Tile و دو Filler Tile برای حفظ ساختاری منسجم وجود دارد. زیر این Tileها، Interposer فعال قرار دارد که به این بستهبندی ساختار سهبعدی میبخشد. نکته جالب اینجاست که اینتل برای تمامی این Tileها بهجز Base Tile از شرکت TSMC استفاده کرده است. Base Tile بهتنهایی با استفاده از لیتوگرافی قدیمی ۲۲ نانومتری ساخته شده است که نشاندهنده تغییرات و نوآوریهای متعدد در طراحی این محصول است.

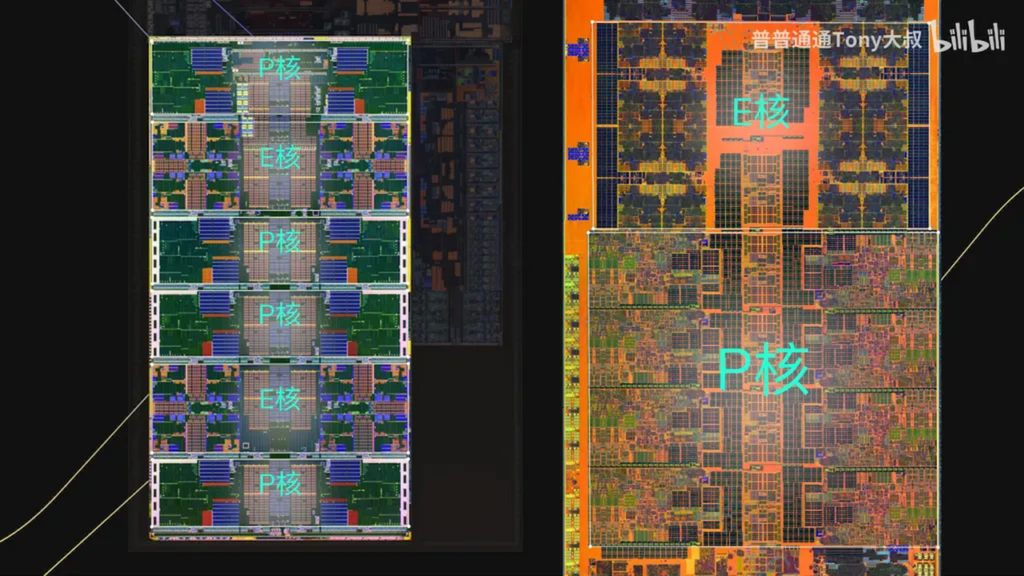

Compute Tile که بخش اصلی فضای Die را به خود اختصاص داده است، میزبان تمامی هستهها و کشهای پردازنده است. مقایسهها نشان میدهند که اندازه هستههای Lion Cove در Arrow Lake بهمراتب کوچکتر از هستههای Raptor Cove است که در نسل سیزدهم پردازندههای اینتل بهکار رفتهاند.

این کاهش اندازه بهدلیل تغییر نود تولید از Intel 7 به TSMC N3B رخ داده است. علاوهبراین، چیدمان هستهها در Arrow Lake بهگونهای است که هستههای عملکردی بهصورت متوالی درکنار هستههای کارآمد قرار گرفتهاند؛ درحالیکه در Raptor Lake این هستهها در مکانهای مختلفی از Die قرار داشتند.

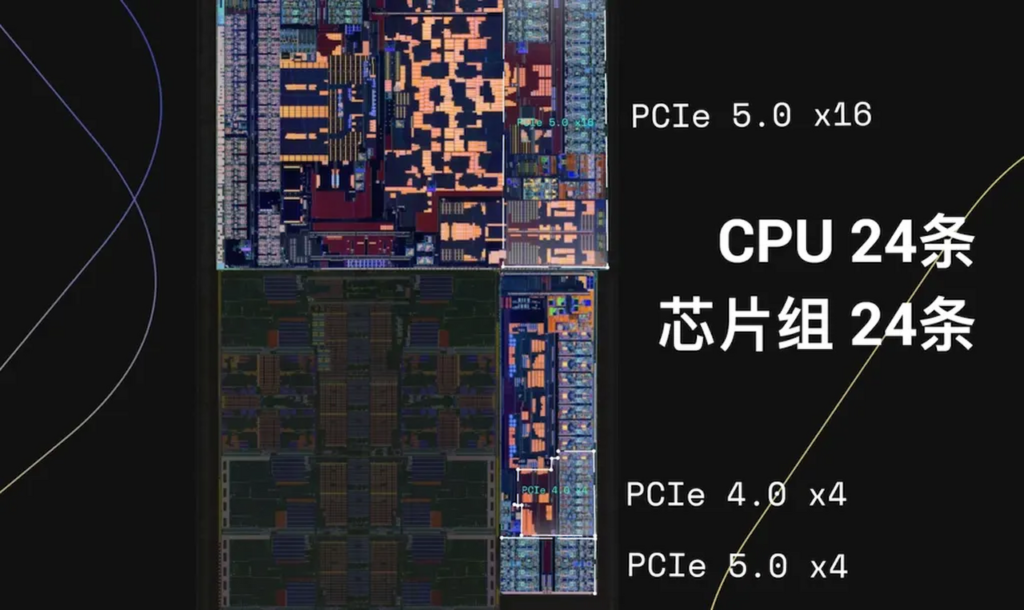

در طراحی جدید Core Ultra 9 285K، ساختار حافظه و کنترلرها به SoC Tile منتقل شدهاند که با استفاده از نود N6 TSMC ساخته شده است. این انتقال تأخیرهایی را بههمراه خواهد داشت و با باس حلقهای که از قبل کند بوده، ممکن است دلیلی برای عملکرد ضعیف Arrow Lake در بازیها باشد. رابط PCIe 5.0 x16 برای GPU در SoC Tile قرار دارد؛ درحالیکه رابطهای PCIe 4.0 و 5.0 x4 برای NVMe SSDها به IOE Tile اختصاص داده شدهاند.

علاوهبراین، SoC Tile شامل NPU Arrow Lake است که گفته میشود با ارائه ۱۳ تاپس عملکرد در حوزه هوش مصنوعی و همراهی با مجتمعهای نمایشگر و رسانه، تواناییهای پیشرفتهای ارائه میدهد. این Tile که در مرکز بسته قرار دارد، بیشترین ارتباطات Die به Die را خواهد داشت؛ زیرا لازم است با تمامی Tileهای دیگر ارتباط برقرار کند. ازآنجاکه اینتل هنوز بهطور رسمی روش اتصال هسته بهغیر هسته را اعلام نکرده است، بهنظر میرسد دادهها همچنان ازطریق باس حلقهای قدیمی منتقل میشوند.

درنهایت، چهار هسته Xe براساس معماری Alchemist به GPU Tile اختصاص داده شدهاند که با استفاده از نود N5 TSMC ساخته شده است. این معماری مشابه Xe-LPG است که در Meteor Lake مشاهده شده و درمقایسهبا Xe2 (Battlemage) در Lunar Lake و Xe-LPG+ (Alchemist+) ضعیفتر است که برای Arrow Lake موبایل پیشبینی شده است.

این رویکرد تجزیهشده به اینتل اجازه میدهد تا به سطحی بالاتر از ماژولاریته دست یابد و هریک از این Tileها را براساس نیازهای خود تغییر دهد. بااینحال، همانطورکه درباره تمامی معماریهای Chiplet یا Tile دیده میشود، این رویکرد به افزایش تأخیر و هزینههای بستهبندی منجر خواهد شد.