بر اساس گزارشهای جدید، شرکت سامسونگ در حال آزمایش یک تراشه از سری اگزینوس بر پایه فرایند ۱.۴ نانومتری است که تمرکز آن بر افزایش کارایی کش قرار دارد.

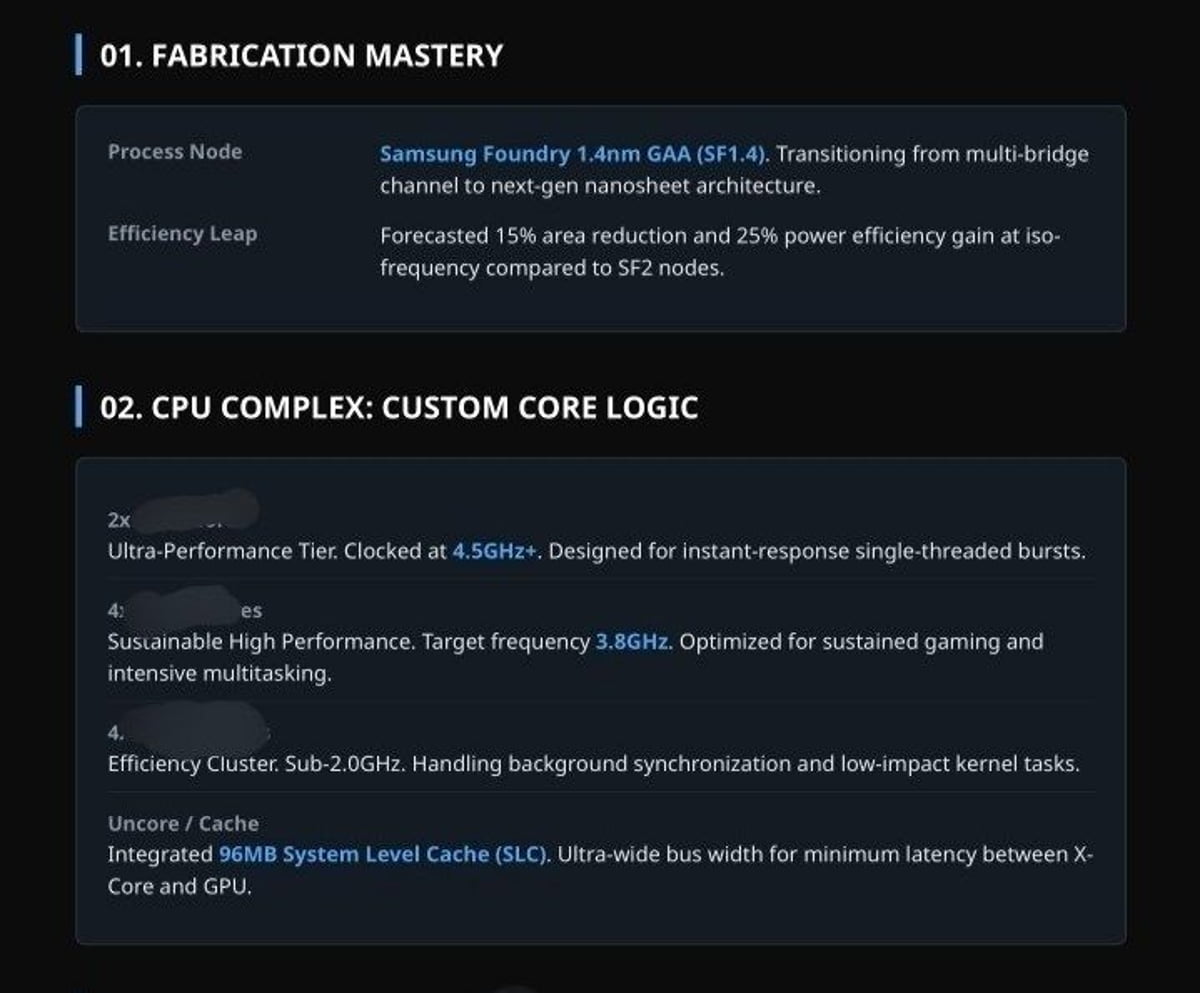

به گزارش سرویس سخت افزار تکناک، فرایند 2 نانومتری GAA هنوز باید چند مرحله دیگر را پشت سر بگذارد تا سامسونگ به فناوری پیشرفته ۱.۴ نانومتری خود اطمینان کامل پیدا کند، اما به این معنا نیست که نمیتواند آزمایشهای اولیه نسل بعدی تراشه اگزینوس (Exynos) خود را روی این فرایند ساخت جدید آغاز کند. جزئیات اولیه مشخصات نشان میدهد که سامسونگ قرار است سقف تازهای برای فرکانسهای حداکثری به همراه داشته باشد و علاوه بر آن، حافظه System Level Cache یا SLC را نیز به رقم خیرهکننده 96 مگابایت برساند.

بهنظر میرسد که اگزینوس ردهبالای آینده همچنان از همان خوشه پردازنده 10 هستهای استفاده خواهد کرد و فرایند ۱.۴ نانومتری سامسونگ نیز 25 درصد بهبود در بهرهوری انرژی به همراه خواهد داشت.

اگزینوس 2700 هنوز معرفی نشده، اما افشاگر SPYGO19726@ جزئیات جالبی از نخستین تراشه ۱.۴ نانومتری سامسونگ منتشر کرده است؛ آن هم در شرایطی که پیشتر شایعاتی درباره دشواریهای سامسونگ در توسعه این فناوری مطرح شده بود؛ مسائلی که گفته میشود شرکت را وادار کرده است تمرکز خود را از رقابت مستقیم با TSMC به سمت فرایند 2 نانومتری و پایداری بیشتر در نرخ بازده تولید معطوف کند. با وجود این، اطلاعات اولیه نشان میدهد اگزینوس جدیدی که با فرایند ۱.۴ نانومتری آزمایش شده است، از یک خوشه پردازنده 10 هستهای با آرایش «2 + 4 + 4» بهره میبرد.

دو هسته Prime با فرکانس 4.50 گیگاهرتز کار میکنند، در حالی که هستههای عملکردی روی فرکانس 3.80 گیگاهرتز قرار دارند و پس از آن چهار هسته کممصرف با فرکانس 2.00 گیگاهرتز فعالیت میکنند. هرچند، شاید چشمگیرترین نکته درباره این تراشه اگزینوس که هنوز نامی برای آن اعلام نشده است، حافظه 96 مگابایتی System Level Cache یکپارچه آن باشد. همچنین SPYGO19726@ به استفاده از پهنای باس فوقعریض برای کاهش تأخیر میان هستههای CPU و GPU اشاره کرده است. حافظه SLC با ذخیره دادههایی که به طور مکرر استفاده میشوند، به کاهش تأخیر حافظه و افزایش پهنای باند کمک میکند.

هرچه این میزان بیشتر باشد، کل سیستم سریعتر و در عین حال بهینهتر عمل خواهد کرد، چرا که اجزایی مانند CPU، GPU، NPU، ISP و دیگر بخشها لازم نیست همواره برای ارسال اطلاعات به این حافظه کش بزرگ فعال باشند. با وجود این، بر اساس گزارش Wccftech، نقطه ضعف این رویکرد آن است که SLC بخش بزرگی از سطح قالب سیلیکونی را اشغال میکند و هرچه این قالب بزرگتر باشد، تولید انبوه چیپست نیز هزینه بیشتری خواهد داشت.

باید در نظر داشت که بیشترین مقدار SLC در تراشههای موبایلی در حال حاضر 10 مگابایت است و این مقدار در Dimensity 9500 دیده میشود. بنابراین افزایش آن به 96 مگابایت، سامسونگ را مجبور میکند قالبی طراحی کند که با ابعاد مناسب گوشیهای هوشمند سازگار نخواهد بود. خوشبختانه کاربردهای دیگری برای چنین تراشهای وجود دارد، اما از آنجا که این موارد تنها مشخصات اولیه هستند، با وجود جذابیت بالا باید فعلاً با کمی احتیاط به آنها نگاه کرد.